隨著電子設備的發展,絕緣型反激式轉換器因其高效率、緊湊結構和良好的隔離特性,在電源管理電路中廣泛應用。這類轉換器在開關過程中易產生電磁干擾(EMI),影響系統的電磁兼容性(EMC)。集成電路設計中的EMC優化不僅關乎設備性能,還涉及法規合規性。本文將探討絕緣型反激式轉換器電路的EMC設計關鍵技巧,聚焦集成電路層面的方法。

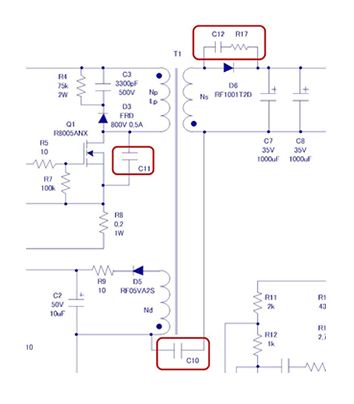

在電路拓撲選擇上,反激式轉換器應優先采用軟開關技術以降低開關噪聲。通過零電壓開關(ZVS)或零電流開關(ZCS)設計,可以顯著減少開關過程中的電壓和電流尖峰,從而抑制高頻EMI。在集成電路中,集成智能開關控制器可以實現精確的時序控制,優化開關行為,減少電磁輻射。

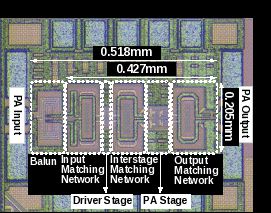

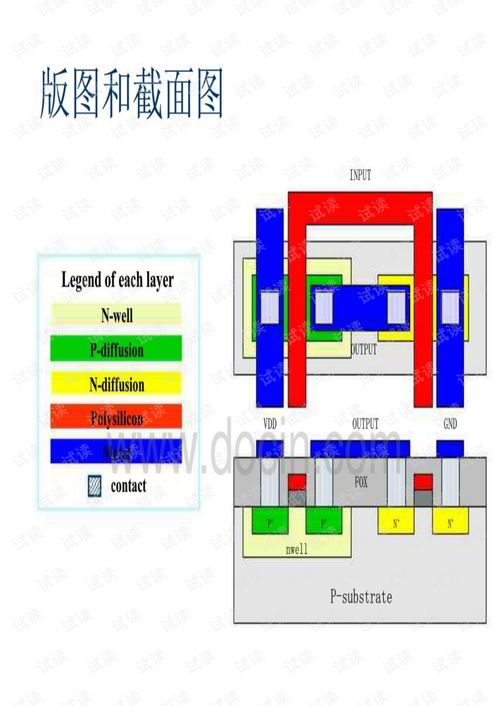

布局和接地設計是EMC優化的核心。在集成電路版圖中,應確保功率開關器件、變壓器和反饋回路的路徑盡可能短,以最小化環路面積和寄生電感。使用多層基板時,將地平面置于關鍵信號層下方,提供低阻抗返回路徑。在反激式轉換器中,變壓器的屏蔽和繞組設計也至關重要;采用靜電屏蔽層可以抑制共模噪聲,而集成電路中的隔離技術(如電容或磁隔離)能增強抗干擾能力。

第三,濾波和去耦策略在EMC設計中不可或缺。在輸入和輸出端集成EMI濾波器,如共模扼流圈和X/Y電容,可有效衰減傳導噪聲。集成電路中,內置有源濾波器或RC網絡能夠吸收高頻開關噪聲。在電源引腳附近放置高頻去耦電容,以減少電壓波動和輻射發射。對于反激式轉換器,在開關節點添加緩沖電路(如RC snubber)可以抑制振鈴現象,進一步降低EMI。

第四,頻率調制技術是另一個有效手段。通過擴頻調制(如dithering)改變開關頻率,可以將EMI能量分散到更寬的頻帶中,從而降低峰值干擾水平。在集成電路設計中,這可以通過集成鎖相環(PLL)或數字控制器實現,確保在滿足效率的同時提升EMC性能。

仿真和測試是驗證EMC設計的關鍵步驟。利用SPICE或專業EMC仿真工具,對絕緣型反激式轉換器電路進行預分析,識別潛在干擾源。集成電路設計階段,應結合電磁場模擬,優化元件布局。實際測試中,遵循標準如CISPR 25,進行輻射和傳導發射測量,并根據結果迭代優化設計。

絕緣型反激式轉換器電路的EMC設計需要從拓撲、布局、濾波、調制和驗證等多個方面入手。通過集成電路的集成化優勢,結合上述技巧,可以顯著提升電磁兼容性,確保設備在各種環境下穩定運行。